# **LOONGSON**

# 龙芯 1C300 处理器用户手册

1.5版

2021年7月

龙芯中科技术股份有限公司

自主决定命运,创新成就未来

# 阅读指南

《龙芯 1C300 处理器用户手册》主要介绍龙芯 1C300 的架构与寄存器描述。关于龙芯 1C300 处理器所集成的 GS232 高性能处理器核的相关资料,请参阅《龙芯 GS232 处理器用户手册》。龙芯 1C300 在本文档中简称龙芯 1C。

# 修订历史

| 日期         | 编辑    | 版本    | 变化                                                    |

|------------|-------|-------|-------------------------------------------------------|

| 2013-3-14  | 研发中心  | 0.0.1 | 初稿                                                    |

| 2013-3-16  | 研发中心  | 0.0.2 |                                                       |

| 2013-3-29  | 研发中心  | 0.0.3 | 补充 DWT、中断配置寄存器描述; CAMIF、<br>UART、OTG 等模块的描述修订         |

| 2013-4-15  | 研发中心  | 0.1   | 地址空间修订                                                |

| 2013-4-26  | 研发中心  | 0.2   |                                                       |

| 2014-2-12  | 研发中心  | 0.3   | 修改排版                                                  |

| 2014-2-28  | 研发中心  | 0.9   | 修改 1C2 改版之后的变动                                        |

| 2014-4-21  | 研发中心  | 1.0   | 增加引脚的上下拉说明<br>增加 SRAM 引脚描述以及修正部分错误<br>芯片名称更新为龙芯 1C300 |

| 2014-6-9   | 研发中心  | 1.1   | 修改手册 GPIO、DMA 等寄存器描述 bug                              |

| 2014-12-12 | 研发中心  | 1.2   | 修正中断位域、CPU 频率配置等寄存器描述<br>bug,修正看门狗基址                  |

| 2015-2-10  | 研发中心  | 1.3   | 修改手册 CAMERA 寄存器描述<br>去除 MAC 1588 支持的描述                |

| 2015-8-4   | 研发中心  | 1.4   | 修正 I2C 复用描述<br>修正 3.1 节中断寄存器部分地址                      |

| 2021-7-7   | 芯片研发部 | 1.5   | 修正表 2-1 中 PLL 配置和 NAND 大小的描述<br>修正部分文字错误,公司信息         |

|            |       |       |                                                       |

手册信息反馈: service@loongson.cn

# 目录

| 1 | 概述    | <u>)</u> |                                       | .10  |

|---|-------|----------|---------------------------------------|------|

|   | 1.1   | 体系结构     | 7框图                                   | .10  |

|   | 1.2   | 芯片主要     | 長功能                                   | . 11 |

|   |       | 1. 2. 1  | 处理器核                                  | 11   |

|   |       | 1. 2. 2  | SDRAM 控制器                             | 11   |

|   |       | 1. 2. 3  | SRAM/NOR FLASH 控制器                    | 11   |

|   |       | 1. 2. 4  | NAND 控制器                              |      |

|   |       | 1. 2. 5  | 时钟发生器                                 |      |

|   |       | 1. 2. 6  | I <sup>2</sup> S 控制器                  |      |

|   |       | 1. 2. 7  | AC97 控制器                              |      |

|   |       | 1. 2. 8  | LCD 控制器                               |      |

|   |       | 1. 2. 9  | Camera 接口                             |      |

|   |       | 1. 2. 10 | MAC 控制器                               |      |

|   |       | 1. 2. 11 | USB2. 0 控制器                           |      |

|   |       | 1. 2. 12 | SPI 控制器                               |      |

|   |       | 1. 2. 13 | 120 控制器                               |      |

|   |       | 1. 2. 14 | UART 控制器                              |      |

|   |       | 1. 2. 15 | GP10.                                 |      |

|   |       | 1. 2. 16 | PWM 控制器                               |      |

|   |       | 1. 2. 17 | RTC.                                  |      |

|   |       | 1. 2. 18 | CAN 控制器                               |      |

|   |       | 1. 2. 19 | SDIO 控制器                              |      |

|   |       | 1. 2. 20 | ADC 控制器                               |      |

| 2 | 引脚    |          | 1T:k3.HH                              |      |

| _ | 2.1   |          |                                       |      |

|   | 2.2   |          |                                       |      |

|   | 2.3   |          | -<br>接口                               |      |

|   | 2.4   |          | IOR FLASH接口                           |      |

|   | 2.5   |          | OKI BEN D                             |      |

|   | 2.6   |          |                                       |      |

|   | 2.7   | 1        | <del>[</del> П                        |      |

|   | 2.8   |          | 口                                     |      |

|   | 2.9   |          |                                       |      |

|   | 2.10  |          |                                       |      |

|   | 2.11  |          | ····································· |      |

|   | 2.12  |          | x 日A 接口                               |      |

|   | 2.13  |          | <b>安</b> 口                            |      |

|   | 2.14  |          | Д                                     |      |

|   | 2.15  |          |                                       |      |

|   | 2.16  |          |                                       |      |

|   | 2.17  |          | ]                                     |      |

|   | 2.17  |          |                                       |      |

|   | 2.19  |          | L F  7                                |      |

|   | 2.19  |          | 号                                     |      |

| 2 |       |          | 1 J                                   |      |

| J | 可付3.1 |          | ·                                     |      |

|   | 3.2   |          | F 存器定义                                |      |

| 1 |       |          | 「什价化义                                 |      |

|   | 4.1   |          |                                       |      |

|   | 4.1   | 町坪朱色     | J                                     | 33   |

|    | 4.2  | 时钟信号     | 说明                           | .33 |

|----|------|----------|------------------------------|-----|

| 5  | 芯片   | 配置与控     | 制                            | .34 |

|    | 5.1  | 地址空间     | 分配                           | .34 |

|    | 5.2  | 芯片配置     | 寄存器(CONFREG)                 | .35 |

|    |      |          | PLL/SDRAM 频率配置寄存器            |     |

|    |      |          | CPU/CAMERA/DC 频率配置寄存器        |     |

|    |      |          | SDRAM 参数寄存器                  |     |

|    |      |          | SHUT_CTRL 寄存器                |     |

|    |      |          | MISC_CTRL 寄存器                |     |

|    |      |          | cpu throt 寄存器                |     |

|    |      |          | UART 复用配置寄存器                 |     |

|    |      |          | GPI00 配置寄存器(对应 GPI0[31:0])   |     |

|    |      |          | GPI01 配置寄存器(对应 GPI0[63:32])  |     |

|    |      |          | GPI02 配置寄存器(对应 GPI0[95:64])  |     |

|    |      |          | GPI03 配置寄存器(对应 GPI0[127:96]) |     |

|    |      |          | PAD[31:0]引脚复用关系配置寄存器         |     |

|    |      |          | PAD[63:32]引脚复用关系配置寄存器        |     |

|    |      |          | PAD[95:64] 引脚复用关系配置寄存器       |     |

|    |      |          | PAD[127:96]引脚复用关系配置寄存器       |     |

|    | 5.3  |          | 寄存器                          |     |

|    |      |          |                              |     |

| Ŭ  | 6.1  |          | н                            |     |

|    | 6.2  |          | 述                            |     |

|    | 6.3  |          | 说明                           |     |

| 7  |      |          | . 90 /4                      |     |

| •  | 7.1  |          |                              |     |

|    | 7.2  |          | 哭<br>俗                       |     |

| 8  |      |          | н                            |     |

| Ū  | 8.1  |          |                              |     |

|    | 8.2  |          |                              |     |

|    | 8.3  |          | i述                           |     |

|    | 8.4  |          |                              |     |

|    | 0    |          | 访存方式                         |     |

|    |      |          | 配置顺序                         |     |

| 9  | I2S  |          | NO.E./W.                     |     |

| _  | 9.1  |          |                              |     |

|    | 9.2  | —        |                              |     |

|    | 9.3  |          | 哭                            |     |

|    | 9.4  |          |                              |     |

| 1( |      |          | 器(DC)                        |     |

| -  | 10.1 |          | , nn ( = - )                 |     |

|    | 10.2 |          | 义和说明                         |     |

|    |      | 10. 2. 1 | 帧缓冲配置寄存器                     |     |

|    |      |          | 帧缓冲地址寄存器 0                   |     |

|    |      |          | 帧缓冲地址寄存器 1                   |     |

|    |      | 10. 2. 4 | 帧缓冲跨度寄存器                     |     |

|    |      | 10. 2. 5 | 颜色抖动配置寄存器                    |     |

|    |      |          | 颜色抖动查找表低位寄存器                 |     |

|    |      |          | 颜色抖动查找表高位寄存器                 |     |

|    |      |          | 颜色抖动说明                       |     |

|    |      |          |                              | 74  |

|      |           | 水平显示宽度寄存器                                                                                                              |      |

|------|-----------|------------------------------------------------------------------------------------------------------------------------|------|

|      | 10. 2. 11 | 行同步配置寄存器                                                                                                               | . 74 |

|      | 10. 2. 12 | 垂直显示高度寄存器                                                                                                              | . 74 |

|      | 10. 2. 13 | 场同步配置寄存器                                                                                                               | . 75 |

|      |           | 输出定序说明                                                                                                                 |      |

|      |           | 伽马校正目录寄存器                                                                                                              |      |

|      |           | 伽马校正值寄存器                                                                                                               |      |

|      |           | 伽马校正说明                                                                                                                 |      |

| 11   | •         | 制器                                                                                                                     |      |

| 11.1 | •         | 存器描述                                                                                                                   |      |

|      | 11. 1. 1  | RegisterO (Bus Mode Register)                                                                                          |      |

|      | 11. 1. 2  | Register1 (Transmit Poll Demand Register)                                                                              |      |

|      | 11. 1. 3  | Register2 (Receive Poll Demand Register)                                                                               |      |

|      | 11. 1. 4  | Register3 (Receive Descriptor List Address Register)                                                                   |      |

|      | 11. 1. 5  | Register4 (Transmit Descriptor List Address Register)                                                                  |      |

|      | 11. 1. 6  | Register5 (Status Register)                                                                                            |      |

|      | 11. 1. 7  | Register6 (Operation Mode Register)                                                                                    |      |

|      | 11. 1. 8  | Register7 (Interrupt Enable Register)                                                                                  |      |

|      | 11. 1. 9  | Register8 (Missed Frame and Buffer Overflow Counter Register                                                           |      |

|      |           | Register9 (Receive Interrupt Watchdog Timer Register)                                                                  |      |

|      |           | Register10 (AXI Bus Mode Register)                                                                                     |      |

|      |           | Register11 (AXI Status Register)                                                                                       |      |

|      |           | Register18 (Current Host Transmit Descriptor Register)                                                                 |      |

|      |           | Register19 (Current Host Receive Descriptor Register)<br>Register20 (Current Host Transmit Buffer Address Register).   |      |

|      |           | Register20 (Current Host Transmit Buffer Address Register).  Register21 (Current Host Receive Buffer Address Register) |      |

| 11.2 |           | Registerzi (Gurrent nost Receive builer Address Register)<br>  制器寄存器描述                                                 |      |

| 11.4 | 11. 2. 1  | RegisterO (MAC Configuration Register)                                                                                 |      |

|      | 11. 2. 2  | Register1 (MAC Frame Filter)                                                                                           |      |

|      | 11. 2. 3  | Register2 (Hash Table High Register)                                                                                   |      |

|      | 11. 2. 4  | Register3 (Hash Table Low Register)                                                                                    |      |

|      | 11. 2. 1  | Register4 (GMII Address Register)                                                                                      |      |

|      | 11. 2. 2  | Register5 (GMII Data Register)                                                                                         |      |

|      | 11. 2. 3  | Register6 (Flow Control Register)                                                                                      |      |

|      | 11. 2. 4  | Register7 (VLAN Tag Register)                                                                                          |      |

|      | 11. 2. 5  | Register8 (Version Register)                                                                                           | . 96 |

|      | 11. 2. 6  | Register14 (Interrupt Status Register)                                                                                 | . 97 |

|      | 11. 2. 7  | Register15 (Interrupt Mask Register)                                                                                   | . 98 |

|      | 11. 2. 8  | Register16 (MAC AddressO High Register)                                                                                |      |

|      | 11. 2. 9  | Register17 (MAC AddressO Low Register)                                                                                 |      |

|      |           | Register18 (MAC Address1 High Register)                                                                                |      |

|      |           | Register19 (MAC Address1 Low Register)                                                                                 |      |

|      |           | Register48 (AN Control Register)                                                                                       |      |

|      |           | Register49 (AN Status Register)                                                                                        |      |

|      |           |                                                                                                                        |      |

|      |           | Register51 (Auto-Negotiation Link Partner Ability Register)                                                            |      |

|      |           | Register52 (Auto-Negotiation Expansion Register)                                                                       |      |

|      |           | Register54 (SGMII/RGMII Status Register)                                                                               |      |

|      |           | Register448 (Time Stamp Control Register)                                                                              |      |

|      |           | Register449 (Sub-Second Increment Register)                                                                            |      |

|      | 11 7 70   | Register 450 (System Time - Seconds Register)                                                                          | 106  |

|      | 11.2.21 Register 451 (System Time - Nanoseconds Register)                   | 106   |

|------|-----------------------------------------------------------------------------|-------|

|      | 11.2.22 Register 452 (System Time - Seconds Update Register)                | 107   |

|      | 11.2.23 Register 453 (System Time - Nanoseconds Update Register)            | 107   |

|      | 11.2.24 Register 454 (Time Stamp Addend Register)                           | 107   |

|      | 11.2.25 Register 455 (Target Time Seconds Register)                         | 107   |

|      | 11.2.26 Register 456 (Target Time Nanoseconds Register)                     | 107   |

|      | 11.2.27 Register 457 (System Time - Higher Word Seconds Register)           | 108   |

|      | 11.2.28 Register 458 (Time Stamp Status Register)                           | 108   |

|      | 11.2.29 Register 459 (PPS Control Register)                                 | 109   |

|      | 11. 2. 30 Register 460 (PPS Auxiliary Time Stamp - Nanoseconds Regis<br>109 | ter)  |

|      | 11.2.31 Register 461 (PPS Auxiliary Time Stamp - Seconds Register).         | 109   |

| 11.3 | DMA 描述符                                                                     |       |

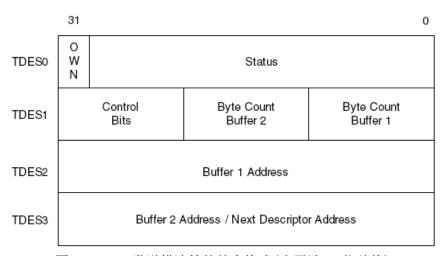

|      | 11.3.1 DMA 描述符的基本格式                                                         | 110   |

|      | <b>11.3.2</b> DMA 接收描述符                                                     | 110   |

|      | 11.3.2.1 RDES0                                                              | . 111 |

|      | 11.3.2.2 RDES1                                                              | . 113 |

|      | 11.3.2.3 RDES2                                                              | . 113 |

|      | 11.3.2.4 RDES3                                                              | . 114 |

|      | 11.3.3 DMA 发送描述符                                                            | 114   |

|      | 11.3.3.1 TDES0                                                              | . 114 |

|      | 11.3.3.2 TDES1                                                              | . 116 |

|      | 11.3.3.3 TDES2                                                              | . 117 |

|      | 11.3.3.4 TDES3                                                              | . 117 |

| 11.4 | 软件编程向导                                                                      | 118   |

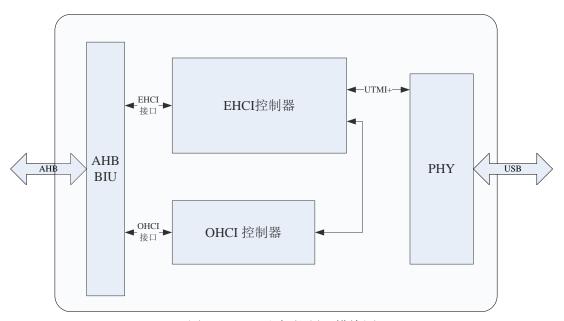

| 12   | USB 控制器                                                                     | .120  |

| 12.1 | 总体概述                                                                        | 120   |

| 12.2 | USB 主机控制器寄存器                                                                | 120   |

|      | <b>12.2.1</b> EHCI 相关寄存器                                                    | 120   |

|      | <b>12.2.2</b> Capability 寄存器                                                | 121   |

|      | <b>12.2.3</b> Operational 寄存器                                               | 121   |

|      | <b>12.2.4</b> EHCI 实现相关寄存器                                                  | 122   |

| 12.3 | OHCI 相关寄存器                                                                  | 124   |

|      | <b>12.3.1</b> Operational 寄存器                                               | 124   |

|      | 12.3.2 OHCI 实现相关寄存器                                                         | 125   |

| 13   | OTG 控制器                                                                     | .127  |

| 13.1 | 概述                                                                          | 127   |

| 13.2 | 寄存器描述                                                                       | 127   |

|      | <b>13.2.1</b> 全局控制与状态寄存器(Global CSR Map)                                    | 128   |

|      | <b>13.2.2</b> Host 模式控制与状态寄存器(Host Mode CSR)                                | 129   |

|      | <b>13.2.3</b> Device 模式控制与状态寄存器(Device Mode CSR)                            | 129   |

|      | 13.2.4 数据 FIFO 访问寄存器组(DFIFO Access Register MAP)                            | 130   |

|      | 13.2.5 功耗控制与门控时钟寄存器组(Power and Clock Gating CSR Map)                        | 131   |

| 13.3 | 寄存器描述                                                                       | 131   |

|      | <b>13.3.1</b> 寄存器访问特性                                                       | 131   |

|      | 13.3.2 全局寄存器                                                                | 131   |

|      | <b>13.3.3</b> Host 模式寄存器                                                    | 156   |

|      | <b>13.3.4</b> Device 模式寄存器                                                  | 167   |

|      | <b>13.3.5</b> 功耗与门控时钟寄存器                                                    | 182   |

| 14   | 通用 DMA                                                                      | .183  |

| 1/11 | DMA 控制哭结构描述                                                                 | 183   |

| 14.2 | DMA 寄     | 存器                                    | 184  |

|------|-----------|---------------------------------------|------|

|      | 14. 2. 1  | ORDER_ADDR_IN                         | 184  |

|      | 14. 2. 2  | DMA ORDER ADDR                        |      |

|      | 14. 2. 3  | DMA_SADDR                             | 185  |

|      | 14. 2. 4  | DMA_DADDR                             |      |

|      | 14. 2. 5  | DMA LENGTH                            |      |

|      | 14. 2. 6  | DMA_STEP_LENGTH                       |      |

|      | 14. 2. 7  | DMA_STEP_TIMES                        |      |

|      | 14. 2. 8  | <br>DMA_CMD                           |      |

| 14.3 | 多个模块      | 央使用 DMA 配置说明                          |      |

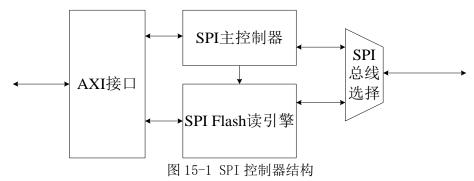

| 15   |           | 制器                                    |      |

| 15.1 |           | 器结构                                   |      |

| 15.2 |           | 子器                                    |      |

|      | 15. 2. 1  | ·····<br>控制寄存器(SPCR)                  |      |

|      | 15. 2. 2  | 状态寄存器 (SPSR)                          |      |

|      | 15. 2. 3  | 数据寄存器(TxFIF0/RxFIF0)                  |      |

|      | 15. 2. 4  | 外部寄存器 (SPER)                          |      |

|      | 15. 2. 5  | 参数控制寄存器 (SFC_PARAM)                   |      |

|      | 15. 2. 6  | 片选控制寄存器(SFC_SOFTCS)                   |      |

|      | 15. 2. 7  | 时序控制寄存器(SFC_TIMING)                   |      |

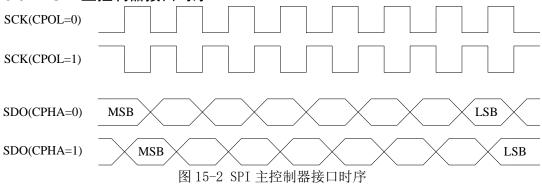

| 15.3 | 接口时序      | · · · · · · · · · · · · · · · · · · · |      |

|      |           | SPI 主控制器接口时序                          |      |

|      |           | SPI Flash 访问时序                        |      |

| 15.4 |           | 到                                     |      |

|      | 15. 4. 1  |                                       |      |

|      | 15. 4. 2  | 硬件 SPI Flash 读                        |      |

|      | 15. 4. 3  | 混合访问 SPI Flash 和 SPI 主控制器             |      |

| 16   | SPI1 控    | 制器                                    |      |

| 16.1 | SPI 主控    | 制器结构                                  | 194  |

| 17   | AC97 控    | 制器                                    | .195 |

| 17.1 | 概述(1C     | 2 无该模块)                               | 195  |

| 17.2 | AC97 控    | 制器寄存器                                 | 195  |

|      | 17. 2. 1  | CSR 寄存器                               | 196  |

|      | 17. 2. 2  | <b>0CC</b> 寄存器                        | 196  |

|      | 17. 2. 3  | ICC 寄存器                               | 197  |

|      | 17. 2. 4  | Codec 寄存器访问命令                         | 197  |

|      | 17. 2. 5  | 中断状态寄存器/中断掩膜寄存器                       | 198  |

|      | 17. 2. 6  | 中断状态/清除寄存器                            | 198  |

|      | 17. 2. 7  | <b>0C</b> 中断清除寄存器                     | 198  |

|      | 17. 2. 8  | IC 中断清除寄存器                            | 199  |

|      | 17. 2. 9  | CODEC WRITE 中断清除寄存器                   | 199  |

|      | 17. 2. 10 | CODEC READ 中断清除寄存器                    | 199  |

| 18   | I2C 控制    | 器                                     | .200 |

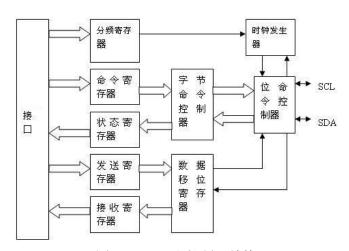

| 18.1 | 概述        |                                       | 200  |

| 18.2 | I2C 控制    | 器结构                                   | 200  |

| 18.3 | I2C 控制    | 器寄存器说明                                | 200  |

|      | 18. 3. 1  | 分频锁存器低字节寄存器(PRERIo)                   | 201  |

|      | 18. 3. 2  | 分频锁存器高字节寄存器(PRERhi)                   | 201  |

|      | 18. 3. 3  | 控制寄存器 (CTR)                           | 201  |

|      | 18. 3. 4  | 发送数据寄存器 (TXR)                         | 201  |

|      | 18. 3. 5  | 接受数据寄存器(RXR)                          | 202  |

|      | 18. 3. 6               | 命令控制寄存器 (CR)                          | 202        |

|------|------------------------|---------------------------------------|------------|

|      | 18. 3. 7               | 状态寄存器 (SR)                            | 202        |

| 19   | UART 挖                 | 2制器                                   | 204        |

| 19.1 | 概述                     |                                       | 204        |

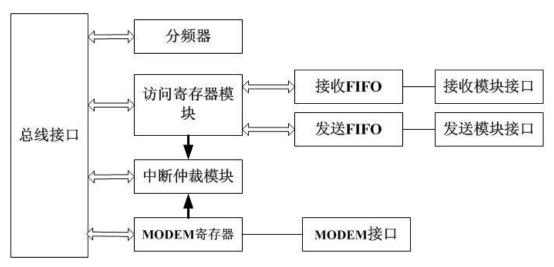

| 19.2 | 控制器组                   | 告构                                    | 204        |

| 19.3 | UARTO S                | SPLIT 配置说明                            | 205        |

| 19.4 | 寄存器指                   | 错述                                    | 206        |

|      | 19. 4. 1               | 数据寄存器(DAT)                            | 206        |

|      | 19. 4. 2               | 中断使能寄存器(IER)                          | 206        |

|      | 19. 4. 3               | 中断标识寄存器(IIR)                          | 207        |

|      | 19. 4. 4               | FIFO 控制寄存器 (FCR)                      | 207        |

|      | 19. 4. 5               | 线路控制寄存器 (LCR)                         | 208        |

|      | 19. 4. 6               | MODEM 控制寄存器(MCR)                      | . 208      |

|      | 19. 4. 7               | 线路状态寄存器 (LSR)                         | 209        |

|      | 19. 4. 8               | MODEM 状态寄存器 (MSR)                     | . 210      |

|      | 19. 4. 9               | 分频锁存器                                 | 210        |

| 19.5 | USART                  | 寄存器描述                                 | 210        |

|      | 19. 5. 1               | 控制寄存器 (CR)                            | . 210      |

|      | 19. 5. 2               | 模式寄存器 (MR)                            | 211        |

|      | 19. 5. 3               | FI/DI 参数寄存器(FIDIR)                    | . 211      |

| 20   | NAND <b></b> 担         | 空制器                                   | 212        |

| 20.1 |                        | 空制器结构描述                               |            |

| 20.2 | NAND ‡                 | 空制器寄存器配置描述                            | 212        |

|      | 20. 2. 1               | 命令寄存器(NAND_CMD)                       |            |

|      | 20. 2. 2               | 页内偏移地址寄存器(ADDR_C)                     |            |

|      | 20. 2. 3               | 页地址寄存器(ADDR_R)                        |            |

|      | 20. 2. 4               | 时序寄存器 (NAND_TIMING)                   |            |

|      | 20. 2. 5               | ID 寄存器(ID_L)                          |            |

|      | 20. 2. 6               | ID 和状态寄存器(STATUS & ID_H)              |            |

|      | 20. 2. 7               | 参数配置寄存器(NAND_PARAMETER)               |            |

|      | 20. 2. 8               | 操作数量寄存器(NAND_OP_NUM)                  |            |

|      | 20. 2. 9               | 映射寄存器 (CS_RDY_MAP)                    |            |

|      |                        | DMA 读写数据寄存器 (DMA_ADDRESS)             |            |

| 20.3 |                        | ADDR 说明                               |            |

| 20.4 |                        | ASH 读写操作举例                            |            |

| 20.5 |                        | CC 说明                                 |            |

| 20.6 |                        | SOOT 说明                               |            |

| 21.1 |                        |                                       |            |

| 21.1 |                        | 描述                                    |            |

| 21.2 | 可行命<br><b>21. 2. 1</b> | ************************************* |            |

|      |                        | SYS_TOYWRITEO.                        |            |

|      |                        | SYS_TOYWRITE1                         |            |

|      | 21. 2. 3               | SYS_TOYREADO                          |            |

|      | 21. 2. 4               | SYS_TOYREAD0 SYS_TOYREAD1             |            |

| 22   |                        | 制器                                    |            |

| 22.1 | 功能概划                   |                                       |            |

| 22.1 |                        | ····································· |            |

| 22.2 |                        |                                       |            |

| 22.4 |                        | z说明                                   |            |

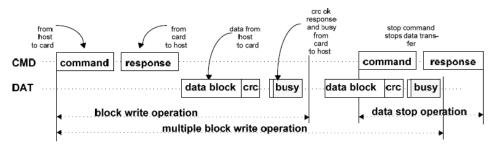

| 22.7 |                        | SD Memory 卡软件编程说明                     | 232<br>232 |

|      | <b>22.4.2</b> SDIO 卡软件编程说明       | 234 |

|------|----------------------------------|-----|

| 23   | CAN 控制器                          | 236 |

| 23.1 | 概述                               | 236 |

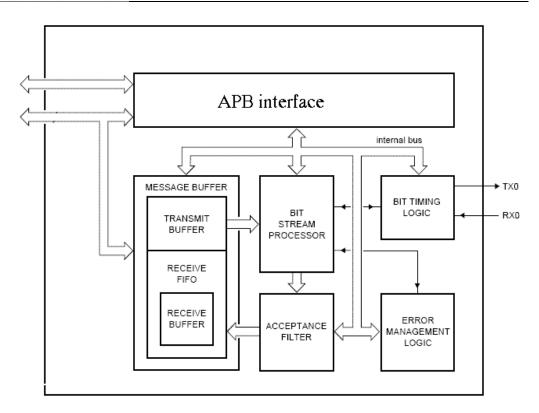

| 23.2 | CAN 控制器结构                        | 236 |

| 23.3 | 标准模式                             | 237 |

|      | 23.3.1 标准模式地址表                   | 237 |

|      | 23.3.2 控制寄存器 (CR)                | 238 |

|      | <b>23.3.3</b> 命令寄存器(CMR)         | 239 |

|      | 23.3.4 状态寄存器 (SR)                | 239 |

|      | 23.3.5 中断寄存器(IR)                 | 239 |

|      | 23.3.6 验收代码寄存器(ACR)              | 240 |

|      | <b>23.3.7</b> 验收屏蔽寄存器(AMR)       | 240 |

|      | 23.3.8 发送缓冲区列表                   | 240 |

|      | 23.3.9 接收缓冲区列表                   | 241 |

| 23.4 | 扩展模式                             | 241 |

|      | 23.4.1 扩展模式地址表                   | 241 |

|      | 23.4.2 模式寄存器(MOD)                | 241 |

|      | 23.4.3 命令寄存器 (CMR)               | 242 |

|      | <b>23.4.4</b> 状态寄存器(SR)          | 242 |

|      | <b>23.4.5</b> 中断寄存器(IR)          | 243 |

|      | <b>23.4.6</b> 中断使能寄存器(IER)       | 243 |

|      | <b>23.4.7</b> 仲裁丢失捕捉寄存器(IER)     | 243 |

|      | <b>23.4.8</b> 错误警报限制寄存器(EMLR)    | 244 |

|      | <b>23.4.9</b> RX 错误计数寄存器(RXERR)  | 245 |

|      | <b>23.4.10</b> TX 错误计数寄存器(TXERR) | 245 |

|      | 23.4.11 验收滤波器                    | 245 |

|      | <b>23.4.12</b> RX 信息计数寄存器(RMCR)  | 245 |

| 23.5 | 公共寄存器                            | 245 |

|      | 23.5.1 总线定时寄存器 0 (BTR0)          | 245 |

|      | 23.5.2 总线定时寄存器 1(BTR1)           | 245 |

|      | 23.5.3 输出控制寄存器(0CR)              | 246 |

| 24   | ADC 控制器                          | 247 |

| 24.1 | 概述                               | 247 |

| 24.2 | 寄存器描述                            | 247 |

| 24.3 | 配置操作                             | 252 |

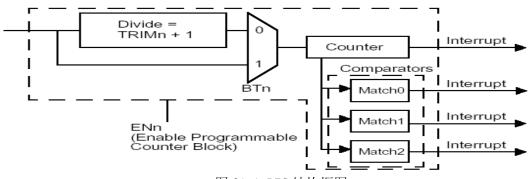

| 25   | PWM 控制器                          | 255 |

| 25.1 | 概述                               |     |

| 25.2 | PWM 寄存器说明                        | 255 |

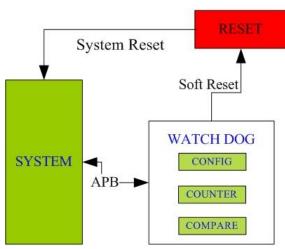

| 26   | 看门狗(WDT)                         | 258 |

| 26.1 | 概述                               | 258 |

| 26.2 | WATCH DOG 寄存器描述                  | 258 |

|      | <b>26.2.1</b> 看门狗使能寄存器(WDT_EN)   | 258 |

|      | <b>26.2.2</b> 看门狗设置寄存器(WDT_SET)  |     |

|      | <b>26.2.3</b> 看门狗计数器(WDT_timer)  |     |

| 27   | 高精度定时器(HCNTR)                    | 260 |

| 27.1 | 概述                               | 260 |

| 27.2 | 安方思世决                            | 260 |

# 图目录

| 图 1-1 力 | 龙芯 1C 结构图                  | 10  |

|---------|----------------------------|-----|

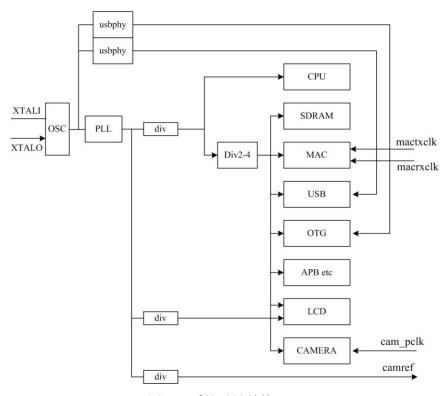

| 图 4-1 差 | 系统时钟结构                     | 33  |

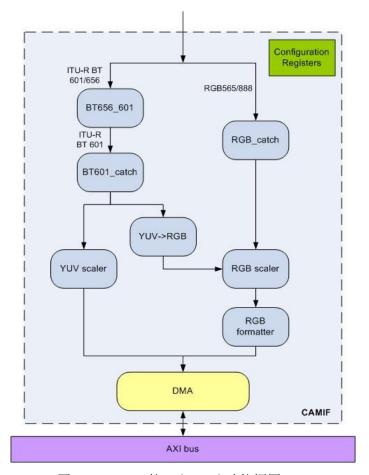

| 图 8-1 ( | Camera 接口(CAMIF)功能框图       | 59  |

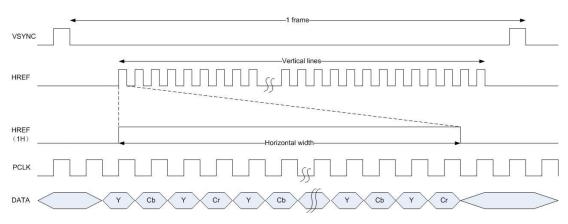

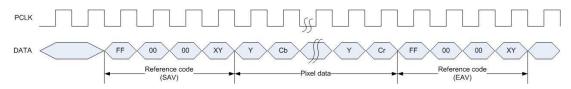

| 图 8-2   | ITU-R BT.601 输入时序          | 60  |

| 图 8-3   | ITU-R BT.656 输入时序          | 60  |

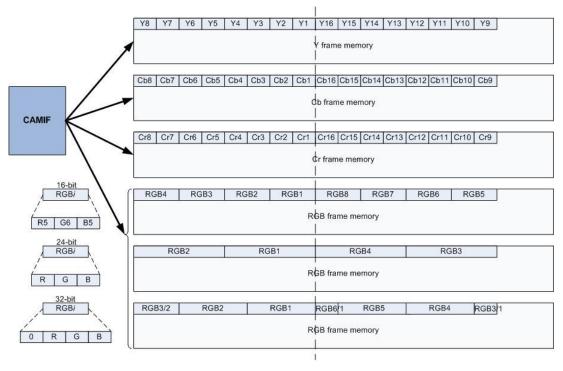

| 图 8-4   | 存储方式                       | 65  |

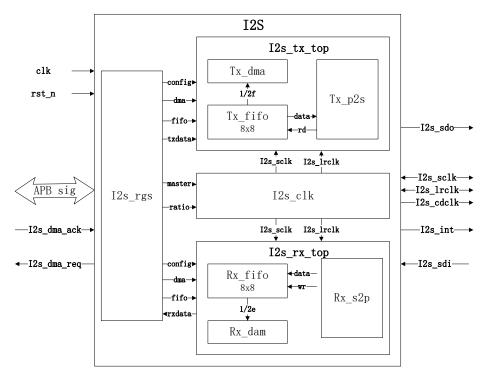

| 图 9-1   | I2S 接口框图                   | 68  |

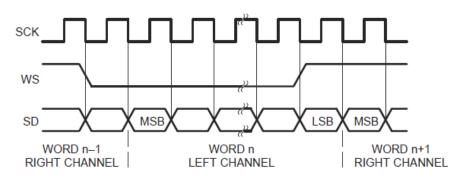

| 图 9-2   | I2S 传输协议                   | 68  |

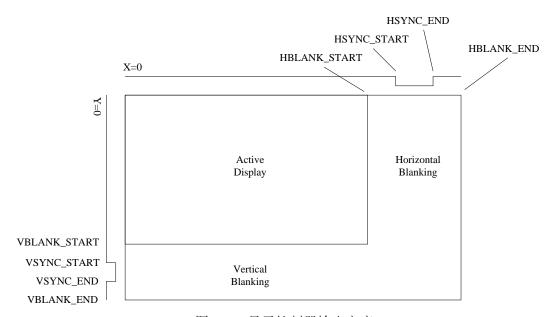

| 图 10-1  | 显示控制器输出定序                  | 75  |

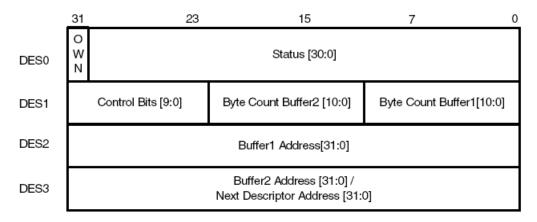

| 图 11-1  | DMA 描述符的基本格式 (小尾端 32 位总线)  | 110 |

| 图 11-2  | DMA 描述符的基本格式 (小尾端 64 位总线)  | 110 |

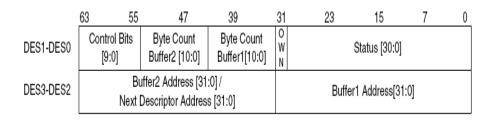

| 图 11-3  | DMA 接收描述符的基本格式(小尾端 32 位总线) | 111 |

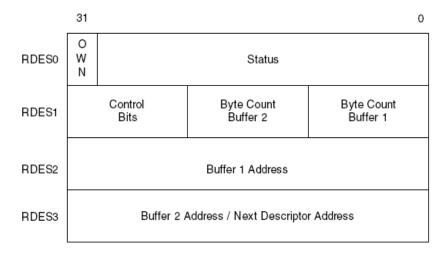

| 图 11-4  | DMA 发送描述符的基本格式(小尾端 32 位总线) | 114 |

| 图 12-1  | USB 主机控制器模块图               | 120 |

| 图 13-1  | OTG CSRs 地址映射              | 128 |

| 图 15-1  | SPI 控制器结构                  | 188 |

| 图 15-2  | SPI 主控制器接口时序               | 190 |

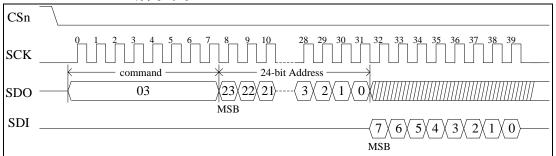

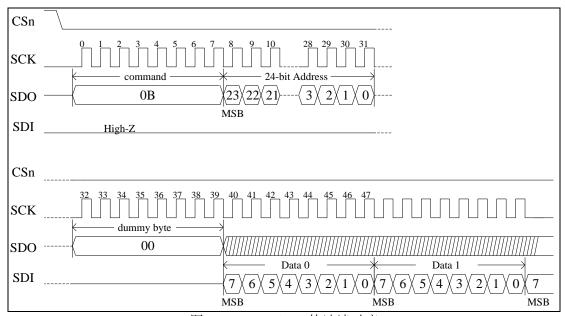

| 图 15-3  | SPI Flash 标准读时序            | 191 |

| 图 15-4  | SPI Flash 快速读时序            | 191 |

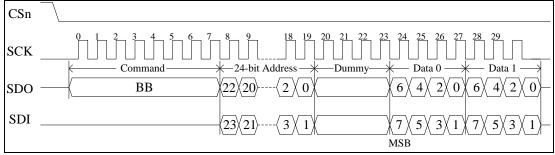

| 图 15-5  | SPI Flash 双向 I/0 读时序       | 191 |

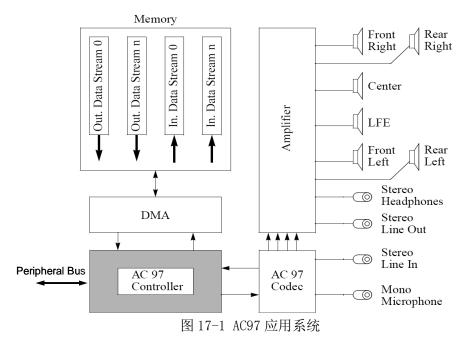

| 图 17-1  | AC97 应用系统                  | 195 |

| 图 18-1  | I2C 主控制器结构                 | 200 |

| 图 19-1  | UART 控制器结构                 | 205 |

| 图 21-1  | RTC 结构框图                   | 220 |

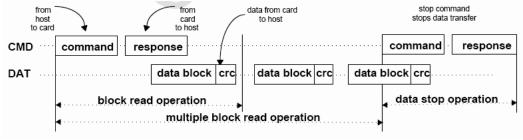

| 图 22-1  | SD 卡多块写操作示意图               | 224 |

| 图 22-2  | SD 卡多块读操作示意图               | 224 |

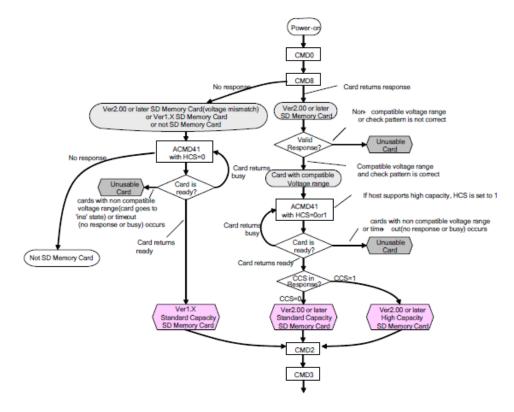

| 图 22-3  | SD Memory 卡初始化流程示意图        | 233 |

| 图 23-1  | CAN 主控制器结构                 | 237 |

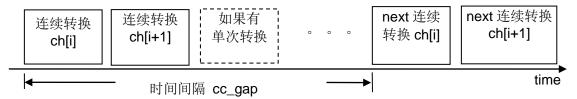

| 图 24-1  | ADC 单次转换/连续转换示意图           | 254 |

| 图 26-1  | 看门狗结构图                     | 258 |

# 表目录

| 表 2-1 信号类型代码              | 16  |

|---------------------------|-----|

| 表 4-1 龙芯 1C 时钟信号          |     |

| 表 8-1 ITU-R BT. 656 基准码   | 60  |

| 表 8-2 第四个字节 XY 值          | 61  |

| 表 15-6 SPI 分频系数           | 189 |

| 表 19-1 UART split 配置及功能复用 | 205 |

| 表 20-1 NAND 地址空间示意图       | 216 |

| 表 22-1 SD 模式下命令格式         | 224 |

# 1 概述

龙芯 1C300(以下简称 1C)芯片是基于 GS232 处理器核的高性价比单芯片系统,可应用于指纹生物识别、物联传感等领域。

1C 包含浮点处理单元,可以有效增强系统浮点数据处理能力。1C 的内存接口,支持多种类型的内存,允许灵活的系统设计。支持 8-bit SLC NAND 或 MLC NAND FLASH,提供高容量的存储扩展接口。

1C 为开发者提供了丰富的外设接口及片上模块,包括 Camera 控制器,USB OTG 2.0 及 USB HOST 2.0 接口,AC97/I2S 控制器,LCD 控制器,ADC 控制器,高速 SPI 接口,全功能 UART 接口等,提供足够的计算能力和多应用的连接能力。片上集成 RTC 功能,可用于实时显示时间。

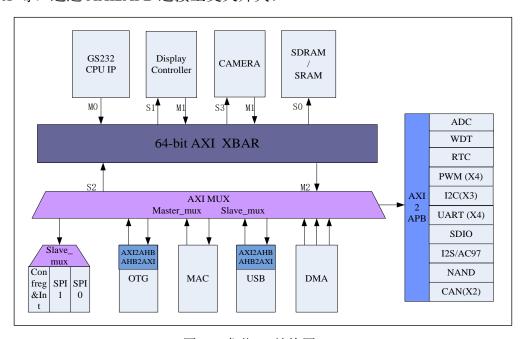

## 1.1 体系结构框图

龙芯 IC 内部采用多级总线结构。处理器核、内存控制器、图形显示控制器、CAMERA 接口模块和 AXI\_MUX 使用交叉开关互连。OTG、MAC、USB、DMA 控制器、SPI 通过 AXI\_MUX 连接至交叉开关。低速外设(I2C、I2S、PWM、UART等)通过 AXI2APB 连接至交叉开关。

图 1-1 龙芯 1C 结构图

## 1.2 芯片主要功能

### 1.2.1 处理器核

- 单核心 GS232, MIPS32 指令集兼容, 主频 300MHZ

- 支持高效双发射(一个时钟节拍执行两条指令)技术

- 支持寄存器重命名、动态调度、转移预测等乱序发射、乱序执行技术

- 五级流水线(取指、译码、发射、执行并写回、提交)微体系结构

- 16KB 数据 cache 和 16KB 指令 cache

- 集成 64 位浮点处理部件,支持全流水的 64 位浮点加法和浮点乘法运算,硬件实现浮点除法运算

### 1.2.2 SDRAM 控制器

- SDRAM 接口,工作频率 45~133MHz

- 支持 8/16 位并行数据总线宽度

- 支持自动刷新和自刷新功能,支持页面模式

## 1.2.3 SRAM/NOR FLASH 控制器

- SRAM 以及 NOR Flash 直连接口,工作频率 66~133MHz

- 支持静态存储器片选引脚,可以单独配置

- 支持 8bit/16bit 并行数据总线宽度

## 1.2.4 NAND 控制器

- 最大支持单颗容量为 4GB NAND FLASH

- 支持 512 字节、2K 字节页、4K 字节页和 8K 字节页类型 FLASH

- 硬件 ECC 生成、检测和指示(软件纠错)

- 支持 FLASH 数据读取速度 8~10MB/S,写入速度 5MB/s

- 支持从 NAND Flash 启动

- 支持小尾端模式

#### 1.2.5 时钟发生器

- 1 个标准 PLL 输入接口,支持外部无源晶体作为芯片时钟输入

- 支持片内输出可配置时钟一路,供片外外设使用

- PLL 频率软件可配置

#### 1.2.6 I<sup>2</sup>S 控制器

- 支持 master 模式下 I<sup>2</sup>S 输入

- 支持 master 模式下 I<sup>2</sup>S 输出

- 支持 8、16、18、20、24、32 位宽

- 支持单声道和立体声道音频数据

- 支持(16、22.05、32、44.1、48)kHz 采样频率

- 支持 DMA 传输模式

#### 1.2.7 AC97 控制器

- 可变采样率 AC97 编解码器接口(48KHz 及以下)

- 支持立体声 PCM 和单声道 MIC 输入

- 支持 2 通道立体声 PCM 输出

- 支持 DMA 和中断操作

- 支持 16、18 和 20 位采样精度,支持可变速率

- 支持 16 位、16 个入口 FIFO 每通道

#### **1.2.8** LCD 控制器

- 支持 16/24 位像素模式

- 支持 RGB444/555/565/888 显示输出

- 支持 1024x768、800x600、640×480、320×240 分辨率

- 支持 DMA 传输模式

#### **1.2.9** Camera 接口

- 支持 ITU-R BT.601/656 8 位输入

- 支持 RAW RGB、RGB565 及 YUV4:2:2 数据输入

- 支持 YUV、RGB888、RGB0888、RGB565 输出

- 支持 320x240 和 640x480 分辨率缩放

- 支持最大 2Kx2K 分辨率输入,分辨率可配置

- 支持 DMA 传输模式

## 1.2.10 MAC 控制器

- 支持 10/100Mbps PHY 器件,包括 10 Base-T、100 Base-TX、100 Base-FX 和 100 Base-T4;

- 完全兼容 IEEE 标准 802.3

- 完全兼容 802.3x 全双工流控和半双工背压流控

- 支持 VLAN 帧

- 支持 DMA 传输模式

- 支持标准的媒体独立接口(MII)

- 支持标准的简化 MII 接口(RMII)可连接外部 PHY 芯片

#### 1.2.11 USB2.0 控制器

- 1 个 USB OTG 2.0 控制器

- 1 个 USB HOST 2.0 控制器

- 支持高速和全速模式

- 支持 DMA 传输模式

- 兼容 USB Rev 1.1 、USB Rev 2.0 协议

#### 1.2.12 SPI 控制器

- 支持两路独立 SPI 接口,每路 SPI 接口均支持 4 个片选

- 遵循串行外设接口(SPI)规范

- 支持同步、串行、全双工通信

- 支持 SPI 主模式

- 每次传输8位

- 支持查询、中断传输模式

- 支持 SPI nor flash 启动

- 支持 SPI 接口双向输入输出,最高数据传输速度 24~96 Mbps

- 支持最低速率通讯要求,速率达 25KB 以下,方便匹配特殊设备。

#### **1.2.13** I<sup>2</sup>C 控制器

- 三路标准 I2C 总线接口

- 支持主、从、或主/从模式配置

- 总线的时钟频率可编程

#### 1.2.14 UART 控制器

- 支持两个全功能串口,其中全功能串口0可复用为4个两线串口或2 个4线串口,支持智能卡协议

- 基于中断操作的 RxD0, TxD0, RxD1, TxD1, RxD2 和 TxD2;

- UART 通道 0, 1 和 2 带 IrDA 1.0

- UART 通道 0 和 1 带 RTS0, CTS0, RTS1 和 CTS1

#### **1.2.15** GPIO

- 最多支持 105 个 GPIO

- 所有 GPIO (启动和系统配置除外) 在复位后默认为输入

- 所有 GPIO 支持中断功能

- 每个 GPIO 管脚均支持电平触发、边沿触发模式,可独立配置

- GPIO 管脚速率可达 4MHz

## 1.2.16 PWM 控制器

- 4路32位可配置PWM定时器

- 支持定时器功能

- 支持计数器功能

### 1.2.17 RTC

- 计时精确到 0.1 秒

- 支持外部无源晶体作为 RTC 时钟输入

- 支持外部电池供电运行,断电后由电池供电

- 专门的电源管脚,可以与电池或者 3.3V 主电源相连

- 提供秒、分、时、日、月、年

## 1.2.18 CAN 控制器

- 2路独立 CAN 控制器

- 兼容 CAN2.0A 和 CAN2.0B 协议(PCA82C200 兼容模式中的无源 扩展帧)

- 支持 CAN 协议扩展

- 位速率可达 1Mbits/s

## 1.2.19 SDIO 控制器

- 1路独立 SDIO 控制器

- 兼容 SD Memory 2.0/MMC/SDIO 2.0 协议

- 支持 SDIO 启动

## **1.2.20** ADC 控制器

- 采样率最高 1MHz

- 4 路 ADC 输入

- 支持 4 线和 5 线触摸屏

- 支持连续采样和单次采样

- 支持模拟看门狗

# 2 引脚定义

## 2.1 约定

本章对龙芯 1C 引脚定义的说明使用以下约定:

信号的输入输出类型由一个代码表示,见表 2-1。

表 2-1 信号类型代码

| 代码       | 描述   |

|----------|------|

| A        | 模拟   |

| DIFF I/O | 双向差分 |

| DIFF IN  | 差分输入 |

| DIFF OUT | 差分输出 |

| I        | 输入   |

| I/O      | 双向   |

| O        | 输出   |

| OD       | 开漏输出 |

| P        | 电源   |

| G        | 地    |

## 2.2 LCD 接口

| 信号名称          | 类型 | 上下拉 | 描述         |

|---------------|----|-----|------------|

| LCD_CLK       | О  | PU  | LCD 时钟信号   |

| LCD_HSYNC     | О  | PU  | LCD 水平同步信号 |

| LCD_VSYNC     | О  | PU  | LCD 垂直同步信号 |

| LCD_EN        | О  | PU  | LCD 使能信号   |

| LCD_DAT[15:0] | О  | PU  | LCD 数据信号   |

【注】在 QFP100 封装下,LCD 接口不能用。在 QFP176 封装下,LCD 可以用 16 位和 24 位模式。16 位模式下引脚不需要复用;在 24 位模式下,低位需要复用 CAM\_DAT[7:0]或者 MAC 信号。

# 2.3 SDRAM 接口

| 信号名称    | 类型 | 上下拉 | 描述                 |

|---------|----|-----|--------------------|

| SD_CLK  | 0  | -   | SDRAM 时钟信号         |

| SD_CKE  | О  | -   | SDRAM 时钟使能信号       |

| SD_CSn  | О  | -   | SDRAM 片选信号,低电平有效   |

| SD_RASn | О  | -   | SDRAM 行选通信号, 低电平有效 |

| SD_CASn | О  | -   | SDRAM 列选通信号, 低电平有效 |

| SD_WE         | О   | - | SDRAM 读写信号, 低电平为写              |

|---------------|-----|---|--------------------------------|

| SD_BA[1:0]    | О   | - | SDRAM 的 Bank 信号,一共 4 个<br>Bank |

| SD_ADDR[12:0] | О   | - | SDRAM 地址信号                     |

| SD_DATA[15:0] | I/O | - | SDRAM 数据信号                     |

| SD_DQM[1:0]   | О   |   | SDRAM 数据屏蔽信号                   |

# 2.4 SRAM/NOR Flash 接口

| 信号名称            | 类型  | 上下拉 | 描述                 |

|-----------------|-----|-----|--------------------|

| SRAM_CSn        | О   | -   | SRAM 片选信号,低点平有效    |

| SRAM_WEn        | О   | -   | SRAM 写使能信号,低电平有效   |

| SRAM_OEn        | О   | -   | SRAM 读使能信号,低电平有效   |

| SRAM_OEn        | О   | -   | SRAM 读使能信号,低电平有效   |

| SRAM_DATA[15:0] | I/O | -   | SRAM 数据信号          |

| SRAM_BHE        | О   |     | SRAM 高 Byte 数据有效信号 |

| SRAM_BLE        | О   |     | SRAM 低 Byte 数据有效信号 |

## 2.5 I2S 接口

| 信号名称     | 类型 | 上下拉 | 描述           |

|----------|----|-----|--------------|

| I2S_MCLK | О  | PU  | I2S 时钟信号     |

| I2S_BCLK | О  | PU  | I2S 比特位时钟信号  |

| I2S_LRCK | О  | PU  | I2S 通道选择信号   |

| I2S_DI   | I  | PU  | I2S 数据串行输入信号 |

| I2S_DO   | О  | PU  | I2S 数据串行输出信号 |

【注】在 QFP100 封装下, I2S 接口没有引出来, 需要和 MAC 引脚复用。在 QFP176 封装下, I2S 接口引出来了,可以直接使用。

# 2.6 I2C 接口

| 信号名称         | 类型  | 上下拉 | 描述                    |

|--------------|-----|-----|-----------------------|

| I2C[2:0]_SCL | О   | PU  | I²C 串行时钟              |

| I2C[2:0]_SDA | I/O | PU  | I <sup>2</sup> C 串行数据 |

【注】在 QFP100 封装下, I2C 接口都没有引出来; QFP176A 封装下引出了 I2C0, 其它的需要通过复用引出。

## 2.7 UART接口

| 信号名称      | 类型 | 上下拉 | 描述            |

|-----------|----|-----|---------------|

| UART0_TX  | О  | PU  | UART0 数据发送    |

| UART0_RX  | I  | PU  | UART0 数据接收    |

| UART0_RTS | I  | PU  | UART0 请求接收    |

| UART0_CTS | I  | PU  | UART0 允许接收    |

| UART0_DSR | I  | PU  | UARTO 设备准备好   |

| UART0_DTR | О  | PU  | UART0 数据终端准备好 |

| UART0_DCD | I  | PU  | UART0 载波检测    |

| UART0_RI  | I  | PU  | UART0 振铃提示    |

【注】在 QFP100 封装下,无全功能串口,只有两线式。在 QFP176D 封装下,全功能串口可直接使用。

## 2.8 PWM 接口

| 信号名称 | 类型 | 上下拉 | 描述        |

|------|----|-----|-----------|

| PWM0 | О  | PU  | PWM0 脉冲输出 |

| PWM1 | О  | PU  | PWM1 脉冲输出 |

| PWM2 | О  | 未引出 | PWM2 脉冲输出 |

| PWM3 | О  | 未引出 | PWM3 脉冲输出 |

【注】在 QFP100 封装下,PWM 没有引出来,需要和其它复用。在 QFP176 封装下,PWM0 和 PWM1 可直接使用,PWM2 和 PWM3 需要和其它复用。

# 2.9 ADC 接口

| 信号名称     | 类型 | 上下拉 | 描述                  |

|----------|----|-----|---------------------|

| ADC_REXT | I  | -   | ADC 参考电阻            |

| ADC_VREF | I  | -   | ADC 参考电压            |

| ADC_VDDA | I  | -   | ADC 模拟电源            |

| ADC_VSSA | I  | -   | ADC 模拟地             |

| ADC_D0   | I  | -   | ADC 第 0 通道采样输入      |

| ADC_D1   | I  | -   | ADC 第 1 通道采样输入      |

| ADC_XP   | I  | _   | 触摸屏 X+/ADC 第2通道采样输入 |

| ADC_YP   | I  | _   | 触摸屏Y+/ADC第3通道采样输入   |

【注】AD接口仅在QFP176A封装下可用。

## 2.10 SPI 接口

| 信号名称         | 类型 | 上下拉 | 描述         |

|--------------|----|-----|------------|

| SPI_SCK      | О  | PU  | SPI 时钟输出   |

| SPI[3:0]_CSn | О  | PU  | SPI 片选 0~3 |

| SPI_MOSI     | О  | PD  | SPI 数据输出   |

| SPI_MISO     | I  | PD  | SPI 数据输入   |

# 2.11 EJTAG 接口

| 信号名称       | 类型 | 上下拉 | 描述                         |

|------------|----|-----|----------------------------|

| EJTAG_SEL  | I  | PU  | JTAG 选择(0: JTAG, 1: EJTAG) |

| JTAG_SEL   | I  | PU  | JTAG 引脚功能复用(为1选择复用<br>功能)  |

| EJTAG_TCK  | I  | PU  | JTAG 时钟                    |

| EJTAG_TDI  | I  | PU  | JTAG 数据输入                  |

| EJTAG_TMS  | I  | PU  | JTAG 模式                    |

| EJTAG_TRST | I  | PU  | JTAG 复位,需下拉                |

| EJTAG_TDO  | О  | PU  | JTAG 数据输出                  |

【注】EJTAG\_SEL 是选择 JTAG 还是 EJTAG, JTAG\_SEL 是用来选择 JTAG 复用功能,不要混淆。

## 2.12 CAMERA 接口

| 信号名称         | 类型 | 上下拉 | 描述        |

|--------------|----|-----|-----------|

| CAM_CLKOUT   | 0  | PU  | 摄像头参考时钟输出 |

| CAM_PCLK_I   | I  | PU  | 摄像头像素时钟输入 |

| CAM_HSYNC    | I  | PU  | 摄像头水平同步信号 |

| CAM_VSYNC    | I  | PU  | 摄像头垂直同步信号 |

| CAMDATA[7:0] | I  | PU  | 摄像头数据输入   |

【注】在QFP100 封装下,CAM 没有引出来,需要和NAND、MAC 复用。 在QFP176 封装下,CAM 可直接使用。

# 2.13 NAND 接口

| 信号名称     | 类型 | 上下拉 | 描述        |

|----------|----|-----|-----------|

| NAND_CLE | О  | PD  | NAND 命令锁存 |

| NAND_ALE    | О   | PD NAND 地址锁存  |             |

|-------------|-----|---------------|-------------|

| NAND_RD     | О   | PD            | NAND 读信号    |

| NAND_WR     | О   | PD NAND 写信号   |             |

| NAND_CE     | О   | PD NAND 片选 0  |             |

| NAND_RDY    | I   | PD NAND 准备好 0 |             |

| NAND_D[7:0] | I/O | PD            | NAND 地址/数据线 |

# 2.14 MAC 接口

| 信号名称         | 类型  | 上下拉         | 描述       |

|--------------|-----|-------------|----------|

| MAC_TXCK     | О   | PU MII 发送时钟 |          |

| MAC_TXEN     | О   | PU          | MII 发送控制 |

| MAC_TXD[3:0] | О   | PU          | MII 发送数据 |

| MAC_RXCK     | I   | PU          | MII 接收时钟 |

| MAC_RXDV     | I   | PU          | MII 接收控制 |

| MAC_RXER     | I   | PU          | MII 接收错误 |

| MAC_RXD[3:0] | I   | PU          | MII 接收数据 |

| MAC_MDCK     | О   | PU          | SMA 接口时钟 |

| MAC_MDIO     | I/O | PU          | SMA 接口数据 |

| MAC_COL      | I   | PU          | MAC 冲突检测 |

| MAC_CRS      | I   | PU          | MAC 载波侦测 |

【注】在 QFP100 封装下,MAC 只能使用 RMII 模式。在 QFP176 封装下,可使用 MII 和 RMII 模式。

# 2.15 OTG 接口

| 信号名称      | 类型       | 上下拉描述          |              |

|-----------|----------|----------------|--------------|

| OTG_DVDD  |          | OTG 数字电源       |              |

| OTG_DVSS  |          | OTG 数字地        |              |

| OTG_VDD33 |          | OTG 模拟电源       |              |

| OTG_VSS33 |          | OTG 模拟地        |              |

| OTG_REXT  |          | OTG 参考电阻       |              |

| OTG_DP    | DIFF I/O | -              | OTG 差分信号线 D+ |

| OTG_DM    | DIFF I/O | - OTG 差分信号线 D- |              |

| OTG_VBUS  |          |                | OTG_VBUS     |

| OTG_ID |  | OTG_ID |

|--------|--|--------|

|--------|--|--------|

# 2.16 USB 接口

| 信号名称      | 类型       | 上下拉描述    |              |

|-----------|----------|----------|--------------|

| USB_DVDD  |          | USB 数字电源 |              |

| USB_DVSS  |          | USB 数字地  |              |

| USB_VDD33 |          | USB 模拟电源 |              |

| USB_VSS33 |          | USB 模拟地  |              |

| USB_REXT  |          | USB 参考电阻 |              |

| USB_DP    | DIFF I/O | -        | USB 差分信号线 D+ |

| USB_DM    | DIFF I/O | -        | USB 差分信号线 D- |

【注】在 QFP100 封装下, USB HOST 不能使用。在 QFP176 封装下,可以使用。

# 2.17 RTC 接口

| 信号名称      | 类型 | 上下拉 | 描述                    |

|-----------|----|-----|-----------------------|

| RTC_CLK_I | I  | -   | RTC 晶振输入,接 32.768K 晶振 |

| RTC_CLK_O | О  | -   | RTC 晶振输出              |

| VR_VDDA   |    |     | RTC 电源                |

# 2.18 时钟配置信号

| 信号名称  | 类型 | 上下拉 | 描述             |

|-------|----|-----|----------------|

| XTALI | I  | -   | 系统时钟晶振输入,接 24M |

| XTAL0 | О  | -   | 系统时钟晶振输出       |

# 2.19 电源地

| 信号名称      | 类型 | 上下拉 | 描述            |

|-----------|----|-----|---------------|

| PLL_VDD33 | P  |     | Core PLL 模拟电源 |

| PLL_VSS33 | G  |     | Core PLL 模拟地  |

| PLL_VDD12 | P  |     | Core PLL 数字电源 |

| PLL_VSS12 | G  |     | Core PLL 数字地  |

| CORE_VDD | P | 核电压电源 |

|----------|---|-------|

| CORE_VSS | G | 核电压地  |

| IO_VDD   | P | IO 电源 |

## 2.20 初始化信号

龙芯 1C 有四种启动方式,OTG、SPI FLASH、NAND FLASH、SDIO。复用功能引脚,通过在系统复位期间采样外部上下拉的值得到配置信息,供软件判定上电状态。

表 2-1 配置信号

| 表 2-1 配置信号  |            |                                                                                                                                                                                                                                                                                                                             |  |

|-------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 引脚名称        | 信号名称       | 描述                                                                                                                                                                                                                                                                                                                          |  |

| NAND_D[3:0] | start_freq | 上电启动时 PLL 倍频配置,频率计算公式为: Freq = 6*(4*NAND_D[3:0] + 40); 当 NAND_D[3:0]=0 时为 bypass 模式, PLL 输出参考时钟 当 NAND_D[3:0]!=0 时, PLL 输出倍频后的时钟 PLL 输出到 CPU 时钟有分频器, 默认二分频 CPU 到 SDRAM 有分频器, 默认二分频                                                                                                                                          |  |

| NAND_D[5:4] | boot_sel   | 启动选择,在 QFP100 和 QFP176 封装下不同 (在 QFP100<br>封装下,NAND 的控制信号没有封装成引脚)<br>在 QFP100 封装下,boot_sel 为<br>00: Reserved<br>01: 表示从 SPI flash 启动<br>10: 表示从 NAND flash 启动(复用 SDRAM 引脚)<br>11: 表示从 NAND flash 启动(复用 MAC 引脚)<br>在 QFP176 封装下,boot_sel 为<br>00: Reserved<br>01: 表示从 SPI flash 启动<br>10: 表示从 SPI flash 启动<br>11: 表示从 SDIO 启动 |  |

| NAND_D[7:6] | nand_type  | NAND boot 时配置 NAND flash 颗粒容量大小<br>11:表示容量大于等于 2Gb(2KB 页/4KB 页/8KB 页)<br>10:表示容量为 1Gb(2KB 页)<br>01:表示容量为 512Mb(512 Bytes 页)<br>00:表示容量为小于等于 256Mb(512 Bytes 页)                                                                                                                                                              |  |

| NAND_CLE    | rs_rd_cfg  | NAND boot 时是否采用 ECC,仅在 boot_sel 选择 NAND flash 启动时有效<br>为 0 时,表示 NAND 非 ECC 启动<br>为 1 时,表示 NAND ECC 启动                                                                                                                                                                                                                       |  |

|          |               | USB_HOST 和 USB_OTG 的时钟选择信号。 |

|----------|---------------|-----------------------------|

| SPI0_CLK | usb_refclksel | 为 1 时,表示由内部的 PLL 提供时钟。      |

|          |               | 为 0 时,表示由外部的晶振提供时钟。         |

# 3 寄存器定义

# 3.1 基本寄存器定义

| 寄存器名称            | 地址          | 读/写<br>(R/W) | 功能描述                    | 复位值        |

|------------------|-------------|--------------|-------------------------|------------|

| 基本寄存器            |             |              |                         |            |

| START_FREQ       | 0xbfe7_8030 | R/W          | PLL 频率配置及<br>SDRAM 分频系数 | 上电状态       |

| CLK_DIV_PARAM    | 0xbfe7_8034 | R/W          | CPU/CAMERA/DC<br>分频系数   | 0x0        |

| CBUS_CONFSIGNALS | 0xbfd0_0400 | R/W          |                         | 0x0        |

| CBUS_SD_CTRL0    | 0xbfd0_0410 | R/W          | SDRAM 参数配置<br>寄存器       | 0x001438a3 |

| CBUS_SD_CTRL1    | 0xbfd0_0414 | R/W          | SDRAM 参数配置<br>寄存器       | 0x80000080 |

| SHUT_CTRL        | 0xbfd0_0420 | R/W          | 各模块开关寄存器                | 0x0        |

| MISC_CTRL        | 0xbfd0_0424 | R/W          | 功能复用寄存器 0               | 0x4        |

| cpu_throt        | 0xbfe7_c010 | R/W          | CPU 动态降频寄存器             | 0x0        |

| 中断寄存器            |             |              |                         |            |

| INTISR0          | 0xbfd0_1040 | R            | 中断状态寄存器 0               | 0x0        |

| INTEN0           | 0xbfd0_1044 | R/W          | 中断使能寄存器 0               | 0x0        |

| INTSET0          | 0xbfd0_1048 | R/W          | 中断置位寄存器 0               | 0x0        |

| INTCLR0          | 0xbfd0_104c | R/W          | 中断清零寄存器 0               | 0x0        |

| INTPOL0          | 0xbfd0_1050 | R/W          | 中断触发电平标志寄存器 0           | 0x0        |

| INTEDGE0         | 0xbfd0_1054 | R/W          | 中断触发边沿标志寄存器 0           | 0x0        |

| INTISR1          | 0xbfd0_1058 | R            | 中断状态寄存器 1               | 0x0        |

| INTEN1           | 0xbfd0_105c | R/W          | 中断使能寄存器 1               | 0x0        |

| INTSET1          | 0xbfd0_1060 | R/W          | 中断置位寄存器 1               | 0x0        |

| INTCLR1   | 0xbfd0_1064                                       | R/W   | 中断清零寄存器 1         | 0x0         |

|-----------|---------------------------------------------------|-------|-------------------|-------------|

| INTOLIXT  | 0XDIUU_1004                                       | IX/VV |                   | UXU         |

| INTPOL1   | 0xbfd0_1068                                       | R/W   | 中断触发电平标志寄存器 1     | 0x0         |

| INTEDGE1  | 0xbfd0_106c                                       | R/W   | 中断触发边沿标志寄存器1      | 0x0         |

| INTISR2   | 0xbfd0_1070                                       | R     | 中断状态寄存器 2         | 0x0         |

| INTEN2    | 0xbfd0_1074                                       | R/W   | 中断使能寄存器 2         | 0x0         |

| INTSET2   | 0xbfd0_1078                                       | R/W   | 中断置位寄存器 2         | 0x0         |

| INTCLR2   | 0xbfd0_107c                                       | R/W   | 中断清零寄存器 2         | 0x0         |

| INTPOL2   | 0xbfd0_1080                                       | R/W   | 中断触发电平标志寄存器 2     | 0x0         |

| INTEDGE2  | 0xbfd0 1084   R/W                                 |       | 中断触发边沿标志<br>寄存器 2 | 0x0         |

| INTISR3   | 0xbfd0_1088 R 中断状态寄存器 3                           |       | 中断状态寄存器 3         | 0x0         |

| INTEN3    | 0xbfd0_108c R/W 中断使能寄存器 3                         |       | 0x0               |             |

| INTSET3   | Oxbfd0_1090 R/W 中断置位寄存器 3                         |       | 0x0               |             |

| INTCLR3   | 0xbfd0_1094 R/W 中断清零寄存器 3                         |       | 0x0               |             |

| INTPOL3   | 0xbfd0_1098                                       | R/W   | 中断触发电平标志<br>寄存器 3 | 0x0         |

| INTEDGE3  | 0xbfd0_109c                                       | 中断触发过 |                   | 0x0         |

| INTISR4   | 0xbfd0_10 <sup>a</sup> 0                          | R     | 中断状态寄存器 4         | 0x0         |

| INTEN4    | 0xbfd0_10 <sup>a</sup> 4                          | R/W   | 中断使能寄存器 4         | 0x0         |

| INTSET4   | 0xbfd0_10 <sup>a</sup> 8                          | R/W   | 中断置位寄存器 4         | 0x0         |

| INTCLR4   | 0xbfd0_10ac                                       | R/W   | 中断清零寄存器 4         | 0x0         |

| INTPOL4   | 0xbfd0_10b0         R/W         中断触发电平标志<br>寄存器 4 |       | 0x0               |             |

| INTEDGE4  | 0xbfd0_10b4 R/W 中断触发<br>寄存器 4                     |       | 中断触发边沿标志寄存器 4     | 0x0         |

| GPIO 寄存器  |                                                   |       |                   |             |

| GPIO_CFG0 | 0xbfd0_10c0                                       | R/W   | GPIO 配置寄存器 0      | 0xffe00040  |

| GPIO_CFG1 | 0xbfd0_10c4                                       | R/W   | GPIO 配置寄存器 1      | 0xfc00_3f3f |

|           | 0xbfd0_10c8                                       | R/W   | GPIO 配置寄存器 2      | 0x1ff0_3fff |

| CDIO CEGS    | 0vbfd0 1000 | R/W   | GPIO 配置寄存器 3   | 0x0         |

|--------------|-------------|-------|----------------|-------------|

| GPIO_CFG3    | 0xbfd0_10cc | TX/VV |                | UXU         |

| GPIO_OE0     | 0xbfd0_10d0 | R/W   | GPIO 输出使能寄存器 0 |             |

| GPIO_OE1     | 0xbfd0_10d4 | R/W   | GPIO 输出使能寄存器 1 | 0xfc00_3f3f |

| GPIO_OE2     | 0xbfd0_10d8 | R/W   | GPIO 输出使能寄存器 2 | 0x1ff0_3fff |

| GPIO_OE3     | 0xbfd0_10dc | R/W   | GPIO 输出使能寄存器 3 | 0x0         |

| GPIO_IN0     | 0xbfd0_10e0 | R/W   | GPIO 输入寄存器 0   | 0x0         |

| GPIO_IN1     | 0xbfd0_10e4 | R/W   | GPIO 输入寄存器 1   | 0x0         |

| GPIO_IN2     | 0xbfd0_10e8 | R/W   | GPIO 输入寄存器 2   | 0x0         |

| GPIO_IN3     | 0xbfd0_10ec | R/W   | GPIO 输入寄存器 3   | 0x0         |

| GPIO_OUT0    | 0xbfd0_10f0 | R/W   | GPIO 输出寄存器 0   | 0x0         |

| GPIO_OUT1    | 0xbfd0_10f4 | R/W   | GPIO 输出寄存器 1   | 0x0         |

| GPIO_OUT2    | 0xbfd0_10f8 | R/W   | GPIO 输出寄存器 2   | 0x0         |

| GPIO_OUT3    | 0xbfd0_10fc | R/W   | GPIO 输出寄存器 3   | 0x0         |

| 复用关系寄存器      |             |       |                |             |

| CBUS_FIRST0  | 0xbfd0_11c0 | R/W   | 第一复用寄存器 0      | 0x0         |

| CBUS_FIRST1  | 0xbfd0_11c4 | R/W   | 第一复用寄存器 1      | 0x0         |

| CBUS_FIRST2  | 0xbfd0_11c8 | R/W   | 第一复用寄存器 2      | 0x0         |

| CBUS_FIRST3  | 0xbfd0_11cc | R/W   | 第一复用寄存器 3      | 0x0         |

| CBUS_SECOND0 | 0xbfd0_11d0 | R/W   | 第二复用寄存器 0      | 0x0         |

| CBUS_SECOND1 | 0xbfd0_11d4 | R/W   | 第二复用寄存器 1      | 0x0         |

| CBUS_SECOND2 | 0xbfd0_11d8 | R/W   | 第二复用寄存器 2      | 0x0         |

| CBUS_SECOND3 | 0xbfd0_11dc | R/W   | 第二复用寄存器 3      | 0x0         |

| CBUS_THIRD0  | 0xbfd0_11e0 | R/W   | 第三复用寄存器 0      | 0x0         |

| CBUS_THIRD1  | 0xbfd0_11e4 | R/W   | 第三复用寄存器 1      | 0x0         |

| CBUS_THIRD2  | 0xbfd0_11e8 | R/W   | 第三复用寄存器 2      | 0x0         |

| CBUS_THIRD3  | 0xbfd0_11ec | R/W   | 第三复用寄存器 3      | 0x0         |

| CBUS_FOURTH0 | 0xbfd0_11f0 | R/W   | 第四复用寄存器 0      | 0x0         |

| CBUS_FOURTH1 | 0xbfd0_11f4 | R/W   | 第四复用寄存器 1      | 0x0         |

|              |             |       |                |             |

| CBUS_FOURTH2  | 0xbfd0_11f8 | R/W | 第四复用寄存器 2 | 0x0 |  |

|---------------|-------------|-----|-----------|-----|--|

| CBUS_FOURTH3  | 0xbfd0_11fc | R/W | 第四复用寄存器 3 | 0x0 |  |

| DMA 配置寄存器     |             |     |           |     |  |

| ORDER_ADDR_IN | 0xbfd0_1160 | R/W | DMA 配置寄存器 |     |  |

# 3.2 各模块寄存器定义

| 寄存器名称            | 地址          | 读/写<br>(R/W) | 功能描述              | 复位值        |  |  |

|------------------|-------------|--------------|-------------------|------------|--|--|

| SDRAM 接口         |             |              |                   |            |  |  |

| SD_CONFIG[31:0]  | 0xbfd0_0410 | R/W          | SDRAM 参数配置<br>寄存器 | 0x30d0db5a |  |  |

| SD_CONFIG[63:32] | 0xbfd0_0414 | R/W          | SDRAM 参数配置<br>寄存器 | 0x50       |  |  |

| PWM0             |             |              |                   |            |  |  |

| CNTR             | 0xbfe5_c000 | R/W          | 主计数器              | 0x0        |  |  |

| HRC              | 0xbfe5_c004 | R/W          | 高脉冲定时参考寄<br>存器    | 0x0        |  |  |

| LRC              | 0xbfe5_c008 | R/W          | 低脉冲定时参考寄<br>存器    | 0x0        |  |  |

| CTRL             | 0xbfe5_c00c | R/W          | 控制寄存器             | 0x0        |  |  |

| PWM1             |             |              |                   |            |  |  |

| CNTR             | 0xbfe5_c010 | R/W          | 主计数器              | 0x0        |  |  |

| HRC              | 0xbfe5_c014 | R/W          | 高脉冲定时参考寄<br>存器    | 0x0        |  |  |

| LRC              | 0xbfe5_c018 | R/W          | 低脉冲定时参考寄<br>存器    | 0x0        |  |  |

| CTRL             | 0xbfe5_c01c | R/W          | 控制寄存器             | 0x0        |  |  |

| PWM2             |             |              |                   |            |  |  |

| CNTR             | 0xbfe5_c020 | R/W          | 主计数器              | 0x0        |  |  |

| HRC              | 0xbfe5_c024 | R/W          | 高脉冲定时参考寄<br>存器    | 0x0        |  |  |

| LRC              | 0xbfe5_c028 | R/W          | 低脉冲定时参考寄<br>存器    | 0x0        |  |  |

| CTRL       | 0xbfe5_c02c | 0xbfe5_c02c R/W 控制        |                | 0x0      |

|------------|-------------|---------------------------|----------------|----------|

| PWM3       | 1           |                           |                |          |

| CNTR       | 0xbfe5_c030 | 0xbfe5_c030 R/W           |                | 0x0      |

| HRC        | 0xbfe5_c034 | R/W                       | 高脉冲定时参考寄<br>存器 | 0x0      |

| LRC        | 0xbfe5_c038 | 0xbfe5_c038 R/W 2         |                | 0x0      |

| CTRL       | 0xbfe5_c03c | R/W                       | 控制寄存器          | 0x0      |

| I2S 接口     |             |                           |                |          |

| IISVersion | 0xbfe6_0000 | R/W                       | I2S 标识寄存器      | 0x0      |

| IISConfig  | 0xbfe6_0001 | R/W                       | I2S 配置寄存器      | 0x0      |

| IISState   | 0xbfe6_0002 | R/W                       | I2S 状态寄存器      | 0x0      |

| IISRxData  | 0xbfe6_0003 | R/W                       | I2S 接收数据寄存器    | 0x0      |

| IISTxData  | 0xbfe6_0004 | R/W                       | I2S 发送数据寄存器    | 0x0      |

| AC97       |             |                           |                |          |

| CSR        | 0xbfe6_0000 | R/W                       | 配置状态寄存器        | 0x0      |

| OCC0       | 0xbfe6_0004 | R/W                       | 输出通道配置寄存器 0    | 0x4141   |

| OCC1       | 0xbfe6_0008 |                           | 保留             |          |

| OCC2       | 0xbfe6_000c |                           | 保留             |          |

| ICC        | 0xbfe6_0010 | Oxbfe6_0010 R/W 输入通道配置寄存器 |                | 0x410000 |

| CODEC_ID   | 0xbfe6_0014 |                           | Codec ID 寄存器   |          |

| CRAC       | 0xbfe6_0018 | Codec 寄存器访问           命令  |                | 0x0      |

| OC0        | 0xbfe6_0020 |                           | 输出声道 0         |          |

| OC1        | 0xbfe6_0024 |                           | 输出声道 1         |          |

| OC2        | 0xbfe6_0028 |                           | 保留             |          |

| OC3        | 0xbfe6_002c |                           | 保留             |          |

| OC4        | 0xbfe6_0030 |                           | 保留             |          |

|            |             | <u></u>                   |                |          |

| 0xbfe6_0034 |                                                                                                                                                                                                                                      | 保留                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 0xbfe6_0038 |                                                                                                                                                                                                                                      | 保留                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

| 0xbfe6_003c |                                                                                                                                                                                                                                      | 保留                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

| 0xbfe6_0040 |                                                                                                                                                                                                                                      | 保留                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

| 0xbfe6_0044 |                                                                                                                                                                                                                                      | 保留                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

| 0xbfe6_0048 |                                                                                                                                                                                                                                      | 保留                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

| 0xbfe6_004c |                                                                                                                                                                                                                                      | 输入声道 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |

| 0xbfe6_0054 | R/W                                                                                                                                                                                                                                  | 中断状态寄存器                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             |

| 0xbfe6_0058 | R/W                                                                                                                                                                                                                                  | 中断掩膜                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0x0         |

| 0xbfe6_005c | R                                                                                                                                                                                                                                    | 中断状态/清除寄存器                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0x0         |

| 0xbfe6_0060 | R                                                                                                                                                                                                                                    | OC 中断清除寄存器                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0x0         |

| 0xbfe6_0064 | R                                                                                                                                                                                                                                    | IC 中断清除寄存器                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0x0         |

| 0xbfe6_0610 | R                                                                                                                                                                                                                                    | CODEC 写中断清<br>除寄存器                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x0         |

| 0xbfe6_006c | R                                                                                                                                                                                                                                    | CODEC 读中断清<br>除寄存器                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x0         |

|             |                                                                                                                                                                                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |

| 0xbfe6_4024 | W                                                                                                                                                                                                                                    | TOY 低 32 位数值<br>写入                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

| 0xbfe6_4028 | W                                                                                                                                                                                                                                    | TOY 高 32 位数值<br>写入                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

| 0xbfe6_402C | R                                                                                                                                                                                                                                    | TOY 低 32 位数值<br>读出                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

| 0xbfe6_4030 | R                                                                                                                                                                                                                                    | <b>TOY</b> 高 <b>32</b> 位数值<br>读出                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |